# **Digital Systems Modeling**

# Chapter 2 VHDL-Based Design

Alain Vachoux Microelectronic Systems Laboratory alain.vachoux@epfl.ch

## Chapter 2: Table of contents

- VHDL overview

- Synthesis with VHDL

- Test bench models & verification techniques

Digital Systems Modeling

## VHDL highlights (1/2)

#### • Hardware description language

- Digital hardware systems

- Modeling, simulation, synthesis, documentation

- IEEE standard 1076 (1987, 1993, 2002)

#### • Originally created for simulation

• IEEE standards 1164 (STD\_LOGIC) and 1076.4 (VITAL)

#### • Further adapted to synthesis

- Language subset

- IEEE standards 1076.3 (packages) and 1076.6 (RTL semantics)

Digital Systems Modeling

## VHDL highlights (2/2)

- Application domain (abstraction levels): Functional -> logic

- Modularity

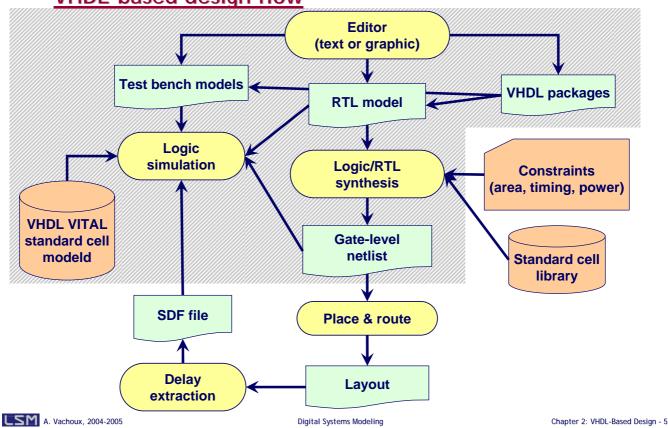

- 5 design entities: entity, architecture, package declaration and body, configuration

- · Separation of interface from implementation

- Separate compilation

#### Strong typing

- · Every object has a type

- Type compatibility checked at compile time

- Extensibility: User-defined types

- Model of time

- Discrete time, integer multiple of some MRT (Minimum Resolvable Time)

- Event-driven simulation semantics

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

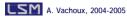

### VHDL-based design flow

The VHDL-based design flow starts from a description of the system as a RTL model. Complex behavior is described as finite state machines or Boolean equations. The RTL model may use external declarations from standard or user-defined packages. The RTL model can be written using a text editor or using a graphical editor supporting flow charts, finite state machines or dataflow representations.

The RTL model can be validated through logic simulation using a VHDL test bench. The test bench declares the design entity to test and stimulus to apply to the unit under test. System functions can then be validated before any realization is actually available.

The RTL model can then be synthesized using a logic synthesizer. The tool is able to derive an optimized gatelevel netlist using logic gates from a standard cell library. The optimization is driven by user-defined constraints on area, timings and/or power consumption. The constraints are not included in the VHDL model, but specified separately in the synthesis tool environment. The standard cell library includes information on all the available cells in some technological process (e.g.  $0.35\mu$  CMOS): logic functions, areas, timing delays, power consumption. The library format is tool dependent.

The gate-level netlist can be described in many forms depending on what to do next. A VHDL version of it is usually used for logic simulation. VHDL models of standard cells are provided by the technology provider (foundry or FPGA vendor) in the form of VITAL models. VITAL is an IEEE standard that defines how VHDL models of cells must be written to allow interoperability between different simulation environments. The logic simulation of gate-level netlists now takes care of cell delays and possibly estimated interconnect delays.

The generation of layout is done with a place and route tool that usually requires a description of the gate-level netlist in a different form (e.g. in Verilog, EDIF or XNF). As layout includes true geometrical information, it is possible to extract the values of parasitic R and C elements from wire shapes and to compute timing delays. These delays are stored in the SDF (Standard Delay Format) format and can be back-annotated in VITAL VHDL models of the standard cells. Logic simulation can now take care of more realistic interconnect delays and can be accurate enough to avoid the need to do time consuming circuit-level (SPICE) simulations.

## VHDL design units

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

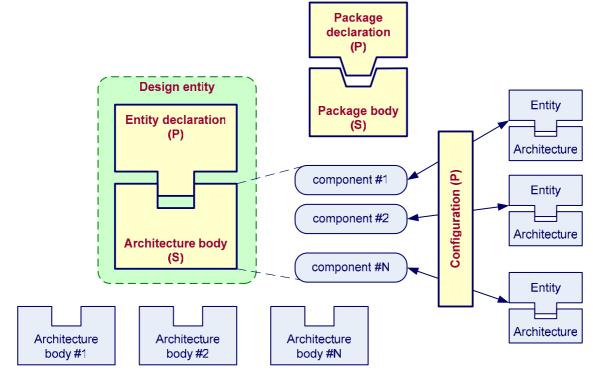

## **Design entity**

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

## Design libraries

- ♦ Context clause:

library library-name {, ...};

use selection {, ...};

- Library names are logical names

- Association to physical locations done outside the VHDL model

- Predefined libraries

- WORK

- STD (incl. STANDARD & TEXTIO packages)

- Implicit context clause:

**library** std, work; **use** std.standard.**all**;

- Clause usage

- STANDARD package defines the type integer

- Variable declaration with full path:

**variable** v: std.standard.integer;

• Variable declaration using context clause:

variable v: integer;

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

## Entity declaration

| <pre>entity entity-name is   [ generic ( parameter-list ) ; ]   [ port ( port-list ) ; ]   [ local-declarations ]</pre> | <pre>param-name {,} : param-type [ := default-value ] ;<br/><br/>param-name {,} : param-type [ := default-value ] ) ;</pre>  |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| <pre>begin { passive-concurrent-statement } ] nd [ entity ] [ entity-name ] ;</pre>                                     | <pre>port (     [ signal ] signal-name {,} : mode signal-type ;      [ signal ] signal-name {,} : mode signal-type ) ;</pre> |

generic (

#### • Example: 1-bit full adder

| entity add1 is<br>generic (                 |                        |

|---------------------------------------------|------------------------|

| TP: time := 0 ns);                          | propagation time       |

| port (                                      |                        |

| <b>signal</b> opa, opb, cin: <b>in</b> bit; | input operands & carry |

| signal sum, cout: out bit);                 | output sum & carry     |

| end entity add1;                            |                        |

Digital Systems Modeling

## Architecture body (1/3)

architecture arch-name of entity-name is

[ local-declarations ]

begin

{ concurrent-statement }

end [ architecture ] [arch-name ];

#### • Example: 1-bit full adder, dataflow (concurrent) behavior

• Design entity: add1(dfl)

$S = A \oplus B \oplus Cin$ Cout = (A•B) + (A•Cin) + (B•Cin)

architecture dfl of add1 is

begin

sum <= opa xor opb xor cin after TP;

cout <= (opa and opb) or (opa and cin) or (opb and cin) after TP;

end architecture dfl;</pre>

Digital Systems Modeling

## Architecture body (2/3)

#### • Example: 1-bit full adder, sequential behavior

• Design entity: add1(algo)

```

architecture algo of add1 is

begin

process (opa, opb, cin)

variable tmp: integer;

begin

tmp := 0;

if opa = '1' then tmp := tmp + 1; end if;

if opb = '1' then tmp := tmp + 1; end if;

if cin = '1' then tmp := tmp + 1; end if;

if tmp > 1 then cout <= '1' after TP;

else cout <= '0' after TP; end if;

if tmp mod 2 = 0 then sum <= '0' after TP; end if;

end process;

end architecture algo;</pre>

```

Digital Systems Modeling

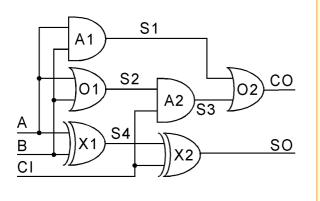

## Architecture body (3/3)

- Example: 1-bit full adder, structural model

- Design entity: add1(str)

- Direct instantiation

| IIIUUEI                                          |

|--------------------------------------------------|

| library gates;<br>architecture str of add1 is    |

|                                                  |

| <b>signal</b> s1, s2, s3, s4: bit;               |

| begin                                            |

| A1: entity gates.and2d1(dfl)                     |

| generic map (TPR => TP)                          |

| <b>port map</b> (i1 => opa, i2 => opb, o => s1); |

| A2: entity gates.and2d1(dfl)                     |

| generic map (TPR => TP)                          |

| <b>port map</b> (i1 => s2, i2 => cin, o => s3);  |

| O1: entity gates.or2d1(dfl)                      |

| generic map (TP)                                 |

| port map (opa, opb, s2);                         |

| O2: entity gates.or2d1(dfl)                      |

| generic map (TP)                                 |

| port map (s3, s1, cout);                         |

| X1: entity gates.ex2d1(dfl)                      |

| generic map (TPR => TP)                          |

| <b>port map</b> (o => s4, i1 => opa, i2 => opb); |

| X2: entity gates.ex2d1(dfl)                      |

| generic map (TP)                                 |

| port map (s4, cin, sum);                         |

| end architecture str;                            |

| ena al chitecture ou,                            |

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

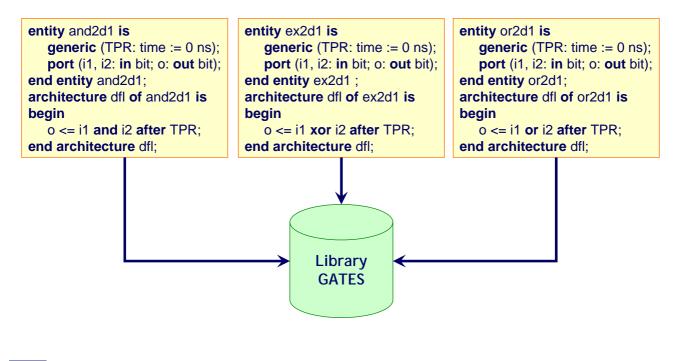

## **Design library**

#### • Example: library GATES

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

| <ul> <li>Testbench</li> <li>Example: 1-bit full adder,<br/>truth table check</li> </ul> | Stimulus_check: process<br>type table_elem is record<br>x, y, ci, co, s: bit;<br>end record;<br>type table is array (0 to 7) of table_elem;<br>constant TT: table :=<br>( x y ci co s<br>('0', '0', '0', '0', '0'), |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| entity tb_add1 is                                                                       | ('0', '0', '1', '0', '1'),                                                                                                                                                                                          |

| end entity tb_add1;                                                                     | ('0', '1', '0', '0', '1'),<br>('0', '1', '1', '1', '0'),                                                                                                                                                            |

|                                                                                         | ('0', '1', '1', '1', '0'),                                                                                                                                                                                          |

| architecture bench of tb_add1 is                                                        | (1', 0', 0', 0', 10', 1),                                                                                                                                                                                           |

| <b>signal</b> op1, op2, ci, sum, co: bit;                                               | ('1', '0', '1', '1', '0'),<br>('1', '1', '0', '1', '0'),                                                                                                                                                            |

| begin                                                                                   | ('1', '1', '1', '1', '1'));                                                                                                                                                                                         |

| UUT: entity work.add1(dfl)                                                              | begin                                                                                                                                                                                                               |

| generic map (TP => 1.2 ns)                                                              | for i in TT'range loop                                                                                                                                                                                              |

| opa => op1,                                                                             | op1 <= TT(i).x;                                                                                                                                                                                                     |

| opb => op2,                                                                             | op 2 <= TT(i).y;                                                                                                                                                                                                    |

| cin => ci,                                                                              | ci <= TT(i).ci;                                                                                                                                                                                                     |

| sum => sum,                                                                             | wait for 5 ns;                                                                                                                                                                                                      |

| cout => co);                                                                            | assert co = TT(i).co and sum = TT(i).s;                                                                                                                                                                             |

|                                                                                         | end loop;                                                                                                                                                                                                           |

|                                                                                         | wait; stop définitif du processus                                                                                                                                                                                   |

|                                                                                         | end process Stimulus_check;                                                                                                                                                                                         |

|                                                                                         | end architecture bench;                                                                                                                                                                                             |

| LSM A. Vachoux, 2004-2005                                                               | Digital Systems Modeling Chapter 2: VHDL-Based Design                                                                                                                                                               |

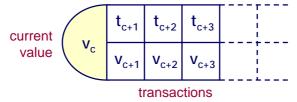

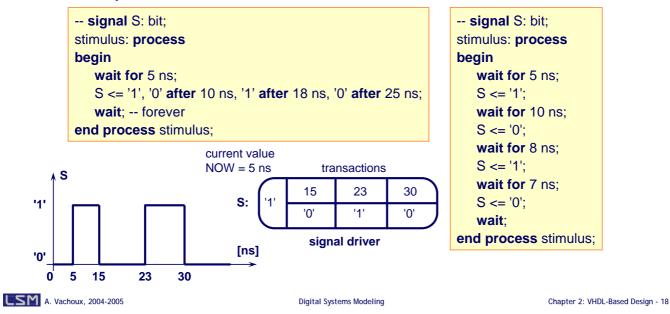

## **Signals**

- Signal declaration: signal signal-name {, ... } : type [ := expression ] ;

- Examples:

| <pre>signal S: bit_vector(15 downto 0);</pre> | default initial value = ( <b>others</b> => '0') |

|-----------------------------------------------|-------------------------------------------------|

| signal CLK: bit := '1';                       | explicit initial value                          |

| signal reset, strobe, enable: boolean;        | default initial value = FALSE                   |

• Signal driver:

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

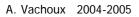

## Process statement

#### Basic concurrent statement:

constant

type

variable

subprogram

[ label : ] process [ ( signal-name { , ... } ) ] [ is ]

{ declaration }

begin

{ sequential-statement }

end process [ label ] ;

#### Process life cycle:

- Created at elaboration time with all its local declarations (e.g. variables)

- Activated/stopped during simulation (variables retain state)

- Destroyed at the end of the simulation

#### Not a subprogram!

Digital Systems Modeling

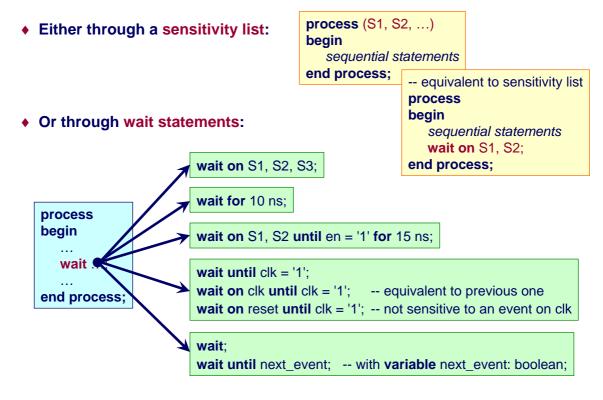

## Process activation control

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

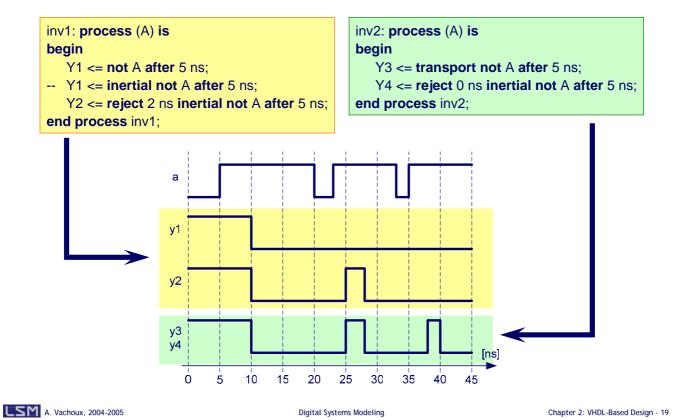

## Signal assignment statement

#### Concurrent or sequential statement:

[ label : ] signal-name <= [ delay-mode ] value-expression [ after time-expression ] {, ... } ;

• Examples:

## **Delay modes**

A. Vachoux 2004-2005

## Signal or variable?

entity shiftreg is

generic (W: positive := 8); -- register width

port (clk, din: in bit; dout: out bit);

end entity shiftreg;

| architecture sig of shiftreg is                        |

|--------------------------------------------------------|

| <pre>signal reg: bit_vector(W-1 downto 0);</pre>       |

| begin                                                  |

| process                                                |

| begin                                                  |

| wait until clk = '1';                                  |

| reg(W-1) <= din;                                       |

| reg(W-2 <b>downto</b> 0) <= reg(W-1 <b>downto</b> 1) ; |

| dout <= reg(0);                                        |

| end process;                                           |

| end architecture sig;                                  |

# architecture var of shiftreg is begin process variable reg: bit\_vector(W-1 downto 0); begin wait until clk = '1'; dout <= reg(0); reg(W-2 downto 0) := reg(W-1 downto 1); reg(W-1) := din; end process; end architecture var;</pre>

Digital Systems Modeling

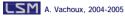

## Initialization & simulation cycle

Digital Systems Modeling

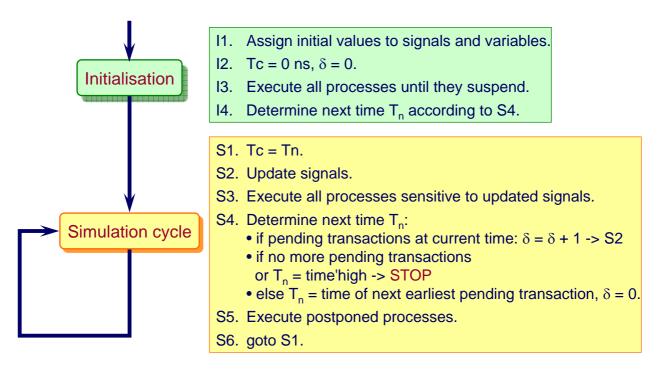

## Zero-delay simulation (delta cycles)

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

| <u>Generic p</u>                                            | <u>arameters</u>                                                                                                                                                                                                                                                                                                                       |              | architecture dfl of addn<br>begin<br>process (cin, opa, opb<br>variable ccin, ccout:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ))                                                                   |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| NB: natural<br>port(<br>opa, opb: ir<br>cin : ir<br>sum : o | 0 ns; propagation time<br>:= 8); word size<br>bit_vector(NB-1 <b>downto</b> 0);<br>bit;<br>ut bit_vector(NB-1 <b>downto</b> 0);<br>t bit)                                                                                                                                                                                              |              | <pre>variable result: bit_ve begin ccout := cin; for i in sum'reverse_i ccin := ccout; result(i) := opa(i) xc ccout := (opa(i) and or (ccin and or (</pre> | ector(sum'range);<br>range <b>loop</b><br>or opb(i) <b>xor</b> ccin; |

| end entity addn;<br>◆ Example:                              | ut bit);<br>entity tb_add32 is<br>end entity tb_add32;<br>architecture bench of th_add                                                                                                                                                                                                                                                 | 32 <b>is</b> | end loop;<br>sum <= result after T<br>cout <= ccout after T<br>end process;<br>end architecture dfl;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                      |

| generic<br>N-bit adder                                      | <pre>architecture bench of tb_add32 is end architecture dfl;<br/>signal opa, opb, sum: bit_vector(31 downto 0);<br/>signal cin, cout: bit;<br/>begin<br/>UUT: entity work.addn(dfl)<br/>generic map (TP =&gt; 2 ns, NB =&gt; opa'length)<br/>port map (opa, opb, cin, sum, cout);<br/> stimulus<br/><br/>end architecture bench;</pre> |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| LSM A. Vachoux, 2004-2005                                   | Digital Systems Modeling                                                                                                                                                                                                                                                                                                               |              | ng                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 2: VHDL-Based Design - 26                                    |

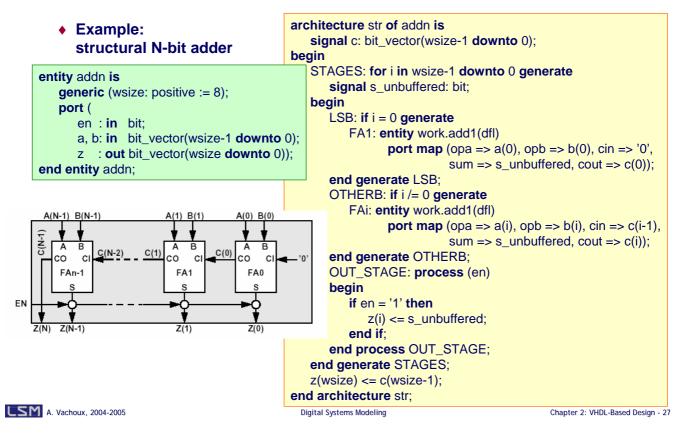

## Generate statement

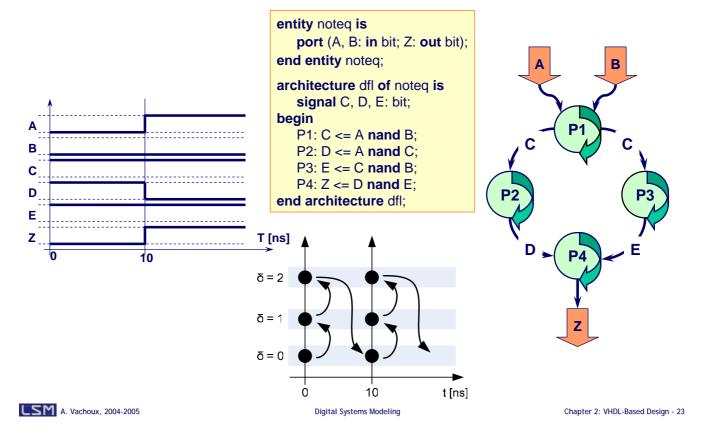

## STD\_LOGIC\_1164 package (1/2)

|                                                           | library ieee;                                |

|-----------------------------------------------------------|----------------------------------------------|

| package STD_LOGIC_1164 is                                 | <b>use</b> ieee.std_logic_1164. <b>all</b> ; |

| type std_ulogic is ('U', un-initialized                   |                                              |

| 'X', forcing unknown                                      |                                              |

| '0', forcing 0                                            |                                              |

| '1', forcing 1                                            |                                              |

| 'Z', high impedance                                       |                                              |

| 'W', weak unknown                                         |                                              |

| 'L', weak 0                                               |                                              |

| 'H', weak 1                                               |                                              |

| '-' don't care);                                          |                                              |

| type std_ulogic_vector is array (natural range <>) of sto | d_ulogic;                                    |

| function resolved (s: std_ulogic_vector) return std_ulog  | jic;                                         |

| <pre>subtype std_logic is resolved std_ulogic;</pre>      |                                              |

| type std_logic_vector is array (natural range <>) of std  | _logic;                                      |

| overloaded logic operators: and, nand, or, nor, xor, x    | nor, not                                     |

| conversion functions: to_bit, to_bitvector, to_stdulogic, | , to_stdlogicvector, to_stdulogicvector      |

| other fonctions                                           |                                              |

| end package STD_LOGIC_1164;                               |                                              |

Digital Systems Modeling

## STD\_LOGIC\_1164 package (2/2)

|                                                               | package body STD_LOGIC_1164 is                  |

|---------------------------------------------------------------|-------------------------------------------------|

|                                                               |                                                 |

|                                                               | type stdlogic_table is                          |

|                                                               | array (std_ulogic, std_ulogic) of std_ulogic    |

|                                                               | constant resolution_table : stdlogic_table := ( |

|                                                               | UX01ZWLH-                                       |

|                                                               | ('U', 'U', 'U', 'U', 'U', 'U', 'U', 'U',        |

|                                                               | ('U', 'X', 'X', 'X', 'X', 'X', 'X', 'X',        |

| function resolved (s : std_ulogic_vector) return std_u        |                                                 |

| <pre>variable result : std_ulogic := 'Z'; default state</pre> | ('U', 'X', 'X', '1', '1', '1', '1', '1', 'X'),  |

| begin                                                         | ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', 'X'),  |

| if s'length = 1 then return s(s'low); single driver           |                                                 |

| else                                                          | ('U', 'X', '0', '1', 'L', 'W', 'L', 'W', 'X'),  |

| for i in s'range loop                                         | ('U', 'X', '0', '1', 'H', 'W', 'W', 'H', 'X'),  |

| result := resolution_table(result, s(i));                     | ('U', 'X', 'X', 'X', 'X', 'X', 'X', 'X',        |

| end loop;                                                     |                                                 |

| end if;                                                       |                                                 |

| return result;                                                |                                                 |

| end function resolved;                                        |                                                 |

|                                                               |                                                 |

| d package body STD_LOGIC_1164;                                |                                                 |

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

## NUMERIC\_STD package

|                                                                                                                                   | library ieee;<br>use ieee.std_logic_1164.all; |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|                                                                                                                                   | use ieee.numeric_std.all;                     |

| <pre>package NUMERIC_STD is     type unsigned is array (natural range &lt;&gt;) of std_logic</pre>                                | ; equivalent to unsigned integer              |

| <pre>type signed is array (natural range &lt;&gt;) of std_logic;</pre>                                                            | equivalent to signed integer                  |

| abs and "-" unary operators arithmetic operators: "+", "-", "*", "/", rem, mod                                                    |                                               |

| relational operators: "<", ">=", "<=", ">=", "/="                                                                                 |                                               |

| <ul> <li> shift and rotate operators: sll, srl, rol, ror</li> <li> logic operators: not, and, or, nand, nor, xor, xnor</li> </ul> |                                               |

| conversion functions:                                                                                                             |                                               |

| <ul> <li>to_integer(arg)</li> <li>to_unsigned(arg, size)</li> </ul>                                                               |                                               |

| to_signed( <i>arg</i> , <i>size</i> )                                                                                             |                                               |

| end package NUMERIC_STD;                                                                                                          |                                               |

Digital Systems Modeling

## VHDL for synthesis

#### Language subset

· All legal VHDL constructs do not have a meaning for synthesis

#### Modeling subset

· Synthesis tools recognize specific code templates to infer hardware

#### • 3 IEEE standards:

- IEEE 1164: 9-state logic type std(u)\_logic(\_vector) + logic operators

- IEEE 1076.3: unsigned and signed types + logic and arith operators

- IEEE 1076.6: synthesis semantics

Digital Systems Modeling

## Supported types: enumerated types

• Types: bit boolean character std\_(u)logic

Default encoding:

type state is (idle, init, shift, add, check);

-- encodage: "000" "001" "010" "011" "100"

Specific encoding, e.g. one-hot:

attribute enum\_encoding: string; attribute enum\_encoding of state: type is "00001 00010 00100 01000 10000"; - idle init shift add check

#### std\_(u)logic (in ieee.std\_logic\_1164)

- Interpreted as 1 bit

- '0', 'L': low logic level

- '1', 'H': high logic level

- 'U', 'X', 'W', '-': metalogical states (ignored)

- 'Z': high-impedance

```

if enable = '1' then

request <= ready;

else

request <= 'Z';

end if;</pre>

```

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 32

Predefined types bit and boolean are interpreted as single bits. Other enumerated types are encoded. Default encoding is binary encoding with enough bits to represent all enumerated states.

When default encoding is not appropriate (e.g. in finite state machine models), it is possible to use a VHDL attribute declaration do annotate each state with its related encoding word. The VHDL attribute enum\_encoding is not predefined and is available in a tool dependent package.

The "one-hot" encoding example shows the 5-bit words defined in a string in the order in which the enumerated states are declared.

The logic types std\_ulogic and std\_logic, defined in the STD\_LOGIC\_1164 standard package, have a specific interpretation for synthesis. Even if they formally have 9 states, they are interpreted in hardware as a single bit. The use of the 'Z' state allows to infer tri-state buffers.

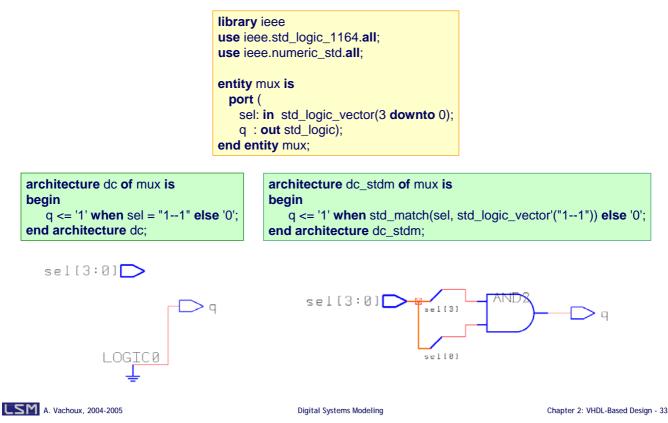

## **STD\_MATCH function**

The (in)equality check involving metalogical states is always interpreted as being false in synthesis, while it is correctly interpreted in simulation. The standard package NUMERIC\_STD defines the function std\_match which should be used as a replacement to the "=" operator to ensure correct interpretation in synthesis.

A comparison with the std\_match function involving don't care states ('-') infers a circuit in which the don't care bits are discarded.

## Integer & array types

- Integer types: integer natural positive

- Infer 32 bit buses by default!

- Highly recommended to use constrained types

-- 7 bits, unsigned **subtype** index **is** natural **range** 0 **to** 63;

-- 8 bits, signed 2's complement subtype my\_byte is integer range -128 to 127;

- Array types: bit\_vector string std\_(u)logic\_vector unsigned signed

- One-dimension array with static integer index ranges and scalar or one-dimension array elements

- "Pack of bits": bit\_vector std\_(u)logic\_vector

- MSB/LSB: unsigned signed (ieee.numeric\_std/\_bit)

- 2-dimension arrays:

library ieee; use ieee.numeric\_std.all; subtype word is unsigned(31 downto 0); -- MSB = word'left = word(31) -- LSB = word'right = word(0) type register\_file is array (0 to 15) of word;

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 34

Values of type integer of derived subtypes natural and positive are by default interpreted as 32-bit busses. It is therefore highly recommended to constraint the ranges to avoid unnecessary large busses. If values in the range are positive, unsigned values are considered. If they may be negative, signed values in 2's complement are considered.

Only one-dimension array types are supported in synthesis. Index ranges must be static, meaning that the range bounds must be known before simulation starts.

The bit\_vector and std\_(u)logic\_vector are interpreted as mere "packs of bits" without any specific meaning (e.g. no MSB/LSB).

The IEEE 1076.3 standard defines the NUMERIC\_BIT and NUMERIC\_STD packages that declare the unsigned and signed array types. The difference between the unsigned (signed) types in the packages is the array element type: bit or std\_logic.

The unsigned type is interpreted (and can be handled) as an unsigned integer. The signed type is interpreted (and can be handled) as a signed integer in 2's complement format. These two types also interpret the bit on the left as the most significant bit (MSB) and the bit on the right as the less significant bit (LSB). The main advantage to use these types is to allow to use arithmetic operations on bit words (which is not possible with the std\_(u)logic\_vector type).

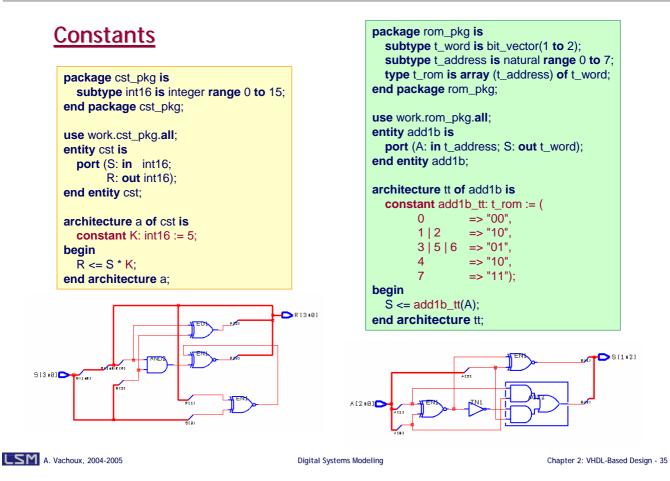

A constant does not infer any hardware so it is highly recommended to use constants as much as possible to minimize area and timings. Constant values are propagated at elaboration time.

Constants can also be used to define ROM content.

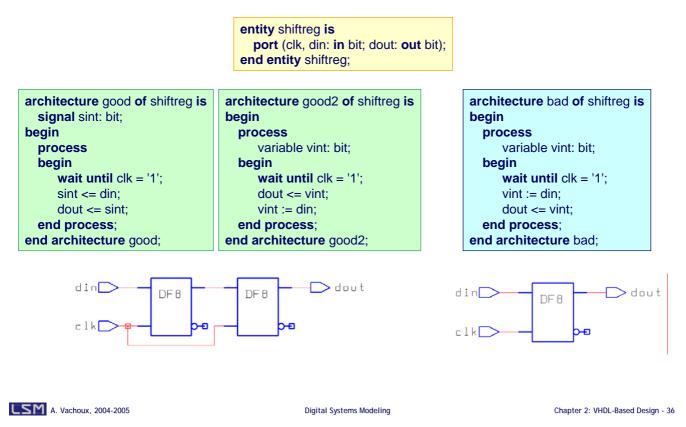

## Variables & signals

Variables and signals have different semantics in VHDL and this difference is conserved in synthesis. Both objects can infer a wire, a register or nothing (the object is optimized out).

Recall that a variable has a scope limited to the process or subprogram in which it is defined, while a signal has a global scope in the whole architecture.

The architectures good and good2 correctly describe a two-bit shift register, while architecture bad infers a 1-bit register. Note that the simulation would give the same results.

# Initial values

| entity E is<br>port (; clk, rst: in bit; );<br>end entity E; |

|--------------------------------------------------------------|

| architecture sync of E is                                    |

| signal S: bit_vector(15 downto 0);                           |

| begin                                                        |

| process                                                      |

| begin                                                        |

| wait until clk = '1';                                        |

| if rst = '1' then                                            |

| S <= ( <b>others</b> => '0');                                |

| + other initializations                                      |

| else                                                         |

| normal behavior                                              |

| end if;                                                      |

| end process;                                                 |

| end architecture sync;                                       |

synchronous reset

```

entity E is

port ( ...; clk, rst: in bit; ... );

end entity E;

architecture async of E is

signal S: bit_vector(15 downto 0);

begin

process (clk, rst)

begin

if rst = '1' then

S \le (others => '0');

-- + other initializations

elsif clk = '1' and clk'event then

-- normal behavior...

end if;

end process:

end architecture async;

```

#### asynchronous reset

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 37

Every VHDL object has an initial value that is either inherited by default from its type or explicitly defined in its declaration. As none of these ways are supported for synthesis, it is required to include explicit initialization code in the model. This is usually done as set/reset behavior and requires the declaration of additional set or reset signals.

A *synchronous reset* checks a reset signal at a clock edge. An *asynchronous reset* can be done independently of the clock signal.

The same approaches can be used for a set signal.

Synchronous designs usually require a way to put the circuit in a known state at power-up or when it is working.

## **Operators**

| Iogical:                                       | or and nor nand xor xnor                | -        |

|------------------------------------------------|-----------------------------------------|----------|

| <ul> <li>Relational <sup>(a)</sup>:</li> </ul> | = /= < (b) > (b) >= (b) <= (b)          |          |

| • Shift & rotate <sup>(c)</sup> :              | sll srl sla sra rol ror                 |          |

| Addition:                                      | + (b) _ (b) & (d)                       | priority |

| • Unary:                                       | + -                                     |          |

| Multiplication:                                | * (b),(e),(f) / (g),(h) mod (g) rem (g) |          |

| Others:                                        | ** (i) abs not                          | +        |

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 38

VHDL operators are supported for synthesis with some limitations:

- (a) Result is of type boolean.

- (b) Can be shared with another operator of the same kind and same priority level.

- (c) Introduced in VHDL-1993. The IEEE 1076.6 standard mentions that they are not supported for synthesis and that the functions SHIFT\_LEFT, SHIFT\_RIGHT, ROTATE\_LEFT and ROTATE\_RIGHT from packages NUMERIC\_BIT/\_STD should be used instead. Synopsys tools however do support them.

- (d) Concatenation operator '&' can be used to emulate shift and rotate operators.

- (e) In general infers a combinational circuit. The inference mechanism depends on the tool (e.g. Synopsys' DesignWare).

- (f) If the right operand is a multiple of 2, infers a simple left shifted register.

- (g) Right operand must be a power of 2.

- (h) If the right operand is a multiple of 2, infers a simple right shifted register.

- (i) Powered operand must be a constant equal to 2.

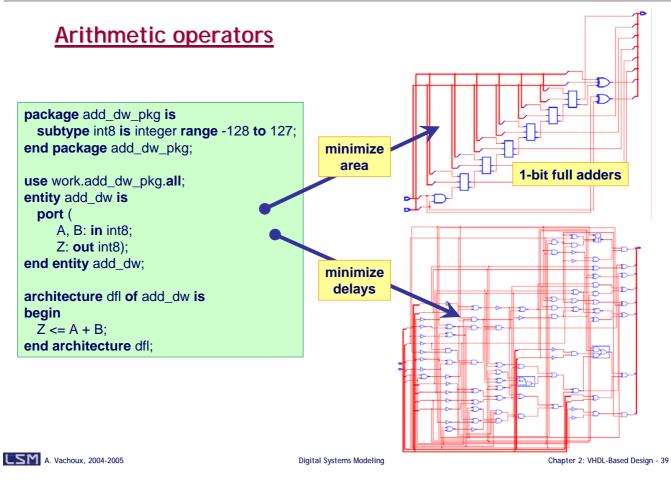

The interpretation of arithmetic operators in synthesis use advanced techniques to select the proper architecture that meets area or timing constraints. Synthesis tools have libraries of synthesizable VHDL models of arithmetic operators (adders, multipliers, etc.) with several architectures.

The simple "+" operator can therefore be mapped to either a serial, small area, carry propagation adder, or to a parallel fast carry look-ahead adder.

The multiply operator "\*" usually infers a combinational circuit.

# **Operator grouping**

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 40

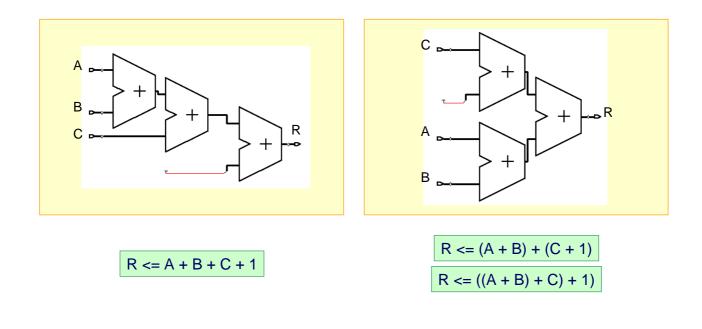

Grouping terms using parentheses allow for overriding the default priority between operator executions. It also allows to infer circuits with different performances.

The given structures are obtained after elaboration but before actual technology mapping took place.

# Resource sharing (1/2)

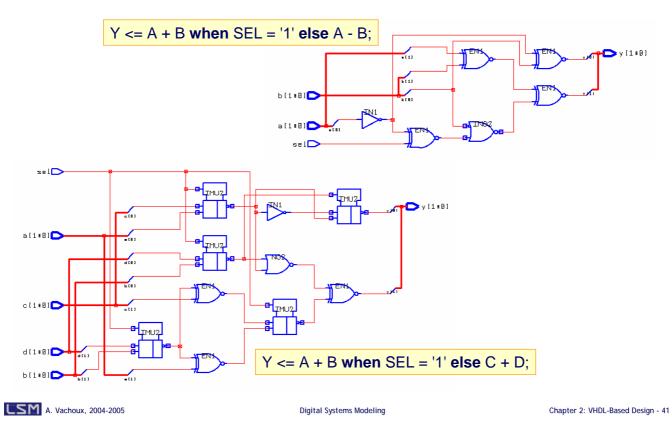

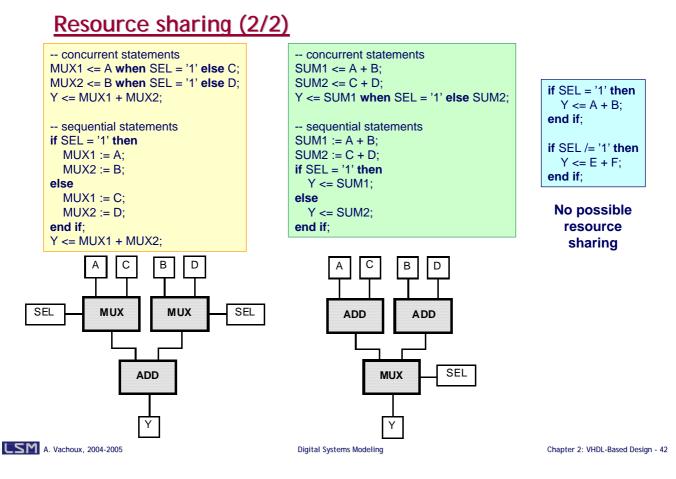

Logic synthesis tools are able to exploit possible sharing of resources such as adders if the VHDL model is written properly. "+", "-", "\*" and "/" operators can be potentially shared, but only addition and subtraction operators are in practice.

The bottom left figure shows the sharing of one adder for two statements. This is possible because the operands are not the same (actually the sharing would work if only one operand is different). Multiplexers are inferred and make the critical path longer at the benefit of a smaller global area.

The top right figure shows another case of resource sharing where operators are the same, but the operations are not. A single add-subtract component is inferred in this case.

The use of VHDL operators can lead to large (combinational) circuits that could not be optimum in term of area or speed. A typical example is the multiplication operator "\*". In these cases it could be worth to use a more detailed model of the operator.

It is possible to control resource sharing by proper VHDL coding. As an example, the concurrent signal assignment statement:

$Y \le A + B$  when SEL = '1' else C + D;

can be rewritten to explicitly mention two multiplexers and one adder or two adders and one multiplexerP.

Resource sharing is possible only for one statement at a time and when the statement is included (or is equivalent to) one process.

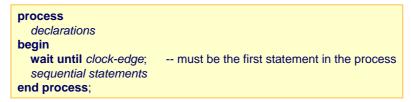

#### **Process**

- A process infers a combinational circuit if and only if all the following conditions are met:

- 1) The process has a sensitivity list

- 2) The process does not declare variables or variables are always assigned before read

- 3) All signals that are read in the process are in the sensitivity list

4) All variables or signals are assigned in every branch of the execution flow (if or case statement)

- Otherwise a sequential circuit is inferred

- Flip-flops are usually required

- Latches are often not required

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 43

The way process statements are written can infer a combinational or a sequential circuit. Combinational circuits have asynchronous behaviors which are only driven by events on signals. Sequential circuits have behaviors which are synchronous to a clock signal and uses flip-flop or latch registers.

The use of concurrent signal assignments always infers combinational circuits.

# **Clock signal inference**

#### • Recognized code templates:

• In if and wait until statements

rising\_edge ( clock-signal-name )

falling\_edge (clock-signal-name)

clock-signal-name 'event and clock-signal-name = '1'

clock-signal-name 'event **and** clock-signal-name = '0'

**not** *clock-signal-name*'stable **and** *clock-signal-name* = '1'

**not** *clock-signal-name*'stable **and** *clock-signal-name* = '0'

• In wait until statement

| clock-signal-name = | '1 | ' |

|---------------------|----|---|

|                     |    |   |

clock-signal-name = '0'

- Signal name does not convey any meaning for synthesis

- Recommended to use meaningful names anyway (e.g. clk)

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 44

# Wait and if statements

Wait statement for inferring behavior sensitive to signal edges

- Several wait statements in a process is legal if and only if they relate to the same (clock) signal and the same rising or falling signal edge

- If statements for inferring behavior sensitive to signal edges or to signal levels

|                           | process (clock-signal-name,)<br>declarations<br>begin                                       |  | process (clock-signal-name,)<br>declarations<br>begin                                         |  |

|---------------------------|---------------------------------------------------------------------------------------------|--|-----------------------------------------------------------------------------------------------|--|

|                           | do not include any statement here<br>if clock-edge then<br>sequential statements<br>end if; |  | do not include any statement here<br>if signal-level then<br>sequential statements<br>end if; |  |

|                           | do not include any statement here end process;                                              |  | do not include any statement here end process;                                                |  |

| LSM A. Vachoux, 2004-2005 | Digital Systems Modeling                                                                    |  | Cł                                                                                            |  |

Chapter 2: VHDL-Based Design - 45

wait statements allow for inferring edge-sensitive sequential elements (flip-flops).

Synchronizing a process on different signals or different edges on the same signal is not supported in synthesis. If this is really needed, several processes must be used.

The use of several wait statements in a process sensitive on the same (clock) signal and on the same signal edge is a way to model finite state machines with implicit states, or sequencers.

if statements also allow for inferring level-sensitive sequential elements (latches).

# Signal assignment Delay clause is ignored S <= '0' after 10 ns; → S <= '0';</li> Delay modes are not allowed reject, inertial Multiple element waveform is not allowed S <= '1', '0' after 20 ns, '1' after 30 ns; -- error</li>

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 46

The right-hand part of the signal assignment can be a literal value (e.g. '0' or '1') or any legal expression that evaluates to a value of the same type as those of the assigned signal.

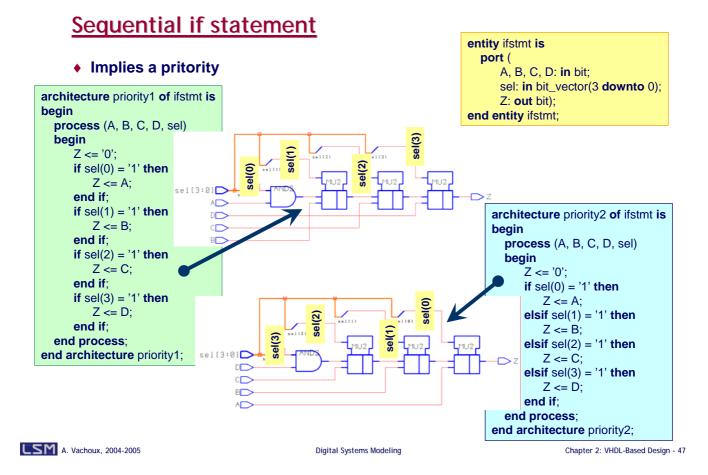

if statements infer multiplexers or equivalent combinational gates and implies priority. How priority is handled depends on the way the statement is written:

- Several cascaded if statements: last branch in the cascade has the higher priority.

- One if statement with several elsif/else alternatives: the first branch has the highest priority.

An assignment similar to " $Z \le 0$ " before the if statement or an else branch prevents inferring unwanted latches:

```

-- priority1

-- priority2

process (...)

process (...)

begin

begin

if sel(0) = '1' then

if sel(0) = '1' then

end if:

elsif sel(3) = '1' then

if sel(3) = '1' then

else

Z <= '0';

...

else

end if:

end process:

Z <= '0':

end if:

end process;

```

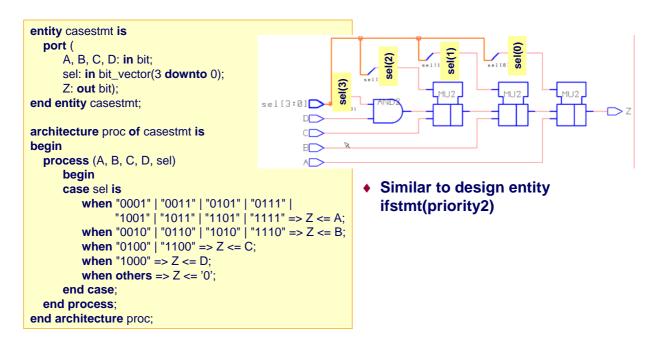

# Sequential case statement

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 48

The case statement also infers circuits with multiplexers or equivalent gates. It is interpreted as an if statement with elsif alternatives

The when others clause is important to prevent inferring unwanted latches.

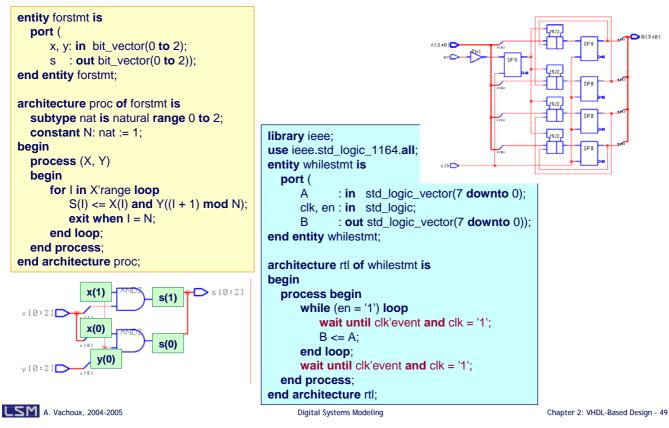

## Loop statements

Loop statements (loop, for, while) are supported for synthesis with some restrictions.

The **for** or **while** statement with static iteration limits duplicates the code in the loop (loop unrolling). Premature loop exits are supported.

There are cases for which a loop statement could be avoided. For example, if we have the following signal declarations:

```

signal S1, S2: bit_vector(1 to 10);

```

then the loop statement:

for i in S1'range loop S2(i) <= S1(i); end loop;

could be rewritten in the more compact form as:

S2 <= S1

When iteration limits are not static, memory elements have to be inferred to store the loop index. A wait statement is therefore required in the loop body.

The infinite loop statement loop ... end loop is interpreted as a while loop whose condition is always true.

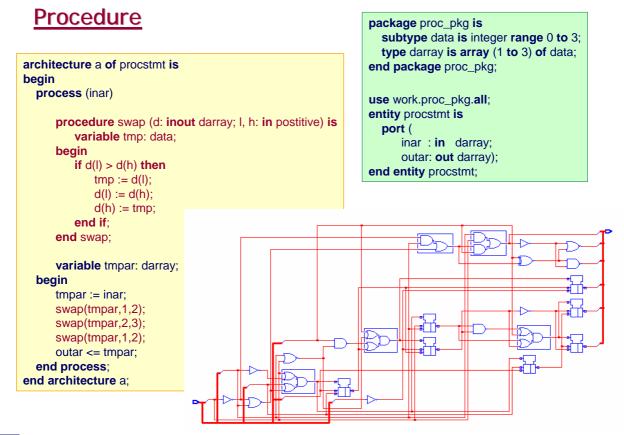

#### **Subprograms**

- Do not infer any structural hierarchy (*z* components)

- A function call always infers a combinational circuit

- Resolution functions and conversion functions are ignored

- A procedure call infers a combinational circuit if and only if:

- 1) Its arguments are of mode in or out

- 2) It does not include any wait statement

- 3) It does not have side effects

Otherwise it infers a sequential circuit

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 50

A function call always infers a combinational circuit since it can only appears in an expression.

A procedure call can infer either a combinational or a sequential circuit. This is valid for both concurrent and sequential forms of the procedure call.

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 51

| Function                                                                                                                                                                                                                                                                                                  | port (                                               | TS: positive := 8);<br>it_vector(NBITS-1 <b>downto</b> 0);<br>it); |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|----------|

| <pre>architecture func of parity_check begin process (data) function parity (bv: bit_vect variable result: bit; begin result := '0'; for i in bv'range loop result := result xor b end loop; return result; end function parity; begin prty &lt;= parity(data); end process; end architecture func;</pre> | tor) <b>return</b> bit <b>is</b><br>∨(i); odd parity | data[3:0]                                                          | ENS prty |

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 52

# **Concurrent statements**

• Signal assignment always infers combinational circuits

-- conditional form (**else** is mandatory) S2 <= (S1 **and** B) **when** CMD = '0' **else** (C **or** D);

- Concurrent procedure call always infers combinational circuits

- · Wait statement not allowed in procedure body

- Do not infer any structural hierarchy

#### Component instance

- · Defines a structural hierarchy which is conserved through synthesis

- Possible operations on components during synthesis: Make instances unique (*uniquify*) Make instances frozen (*don't touch*) Flatten hierarchy (*ungroup*)

- generate statement

- · Both iterative and conditional forms are supported

- Local declarations not supported

LSM A. Vachoux, 2004-2005

The structural hierarchy implied by component instances is conserved through synthesis. It is recommended to use components at the RTL level to ease the management of complex designs. This also eases the definition of timing constraints to critical internal parts of the design.

All instances of the same component usually refer to the same component description. It is required to make each instance unique *uniquify*) to allow individual optimization of each instance.

A component may be synthesized separately and then made frozen (*don't touch*) when synthezising one level up in the hierarchy.

The hierarchy can be flattened (*ungrouped*) during synthesis to allow further optimization across component boundaries.

(C **or** D)

when others;

Chapter 2: VHDL-Based Design - 53

Digital Systems Modeling

# **Miscellaneous**

- Generic parameters

- Of type integer or derived

- Of an enumerated type

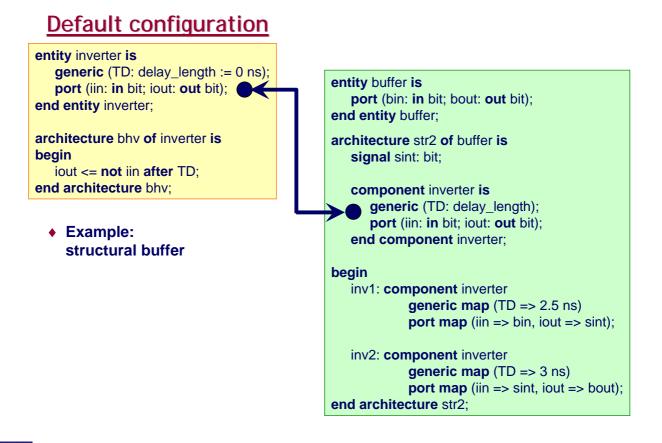

#### Configurations

- Default configuration only

- (Direct instantiation)

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 54

Default configuration means that there is a component declaration that has exactly the same signature as the entity declaration of a design entity in the working library. Signature includes the signal names, modes and types.

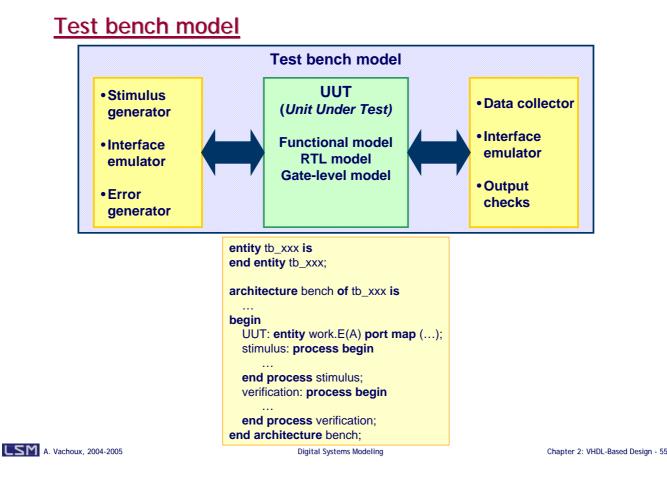

A test bench model aims at validating a functional, RTL or gate-level model. The kind of valifdation depends on the abstraction level of the unit under test:

- Functional model: interface behavior, communication protocol.

- RTL model: design architecture, control and data parts.

- Gate-level model: timings.

A test bench model can be written in VHDL. Three components may be identified:

- A *stimulus generator* whose task is to define the stimulus to apply to the unit under test. Stimulus can be defined in VHDL or in a format closer to the targetted application (e.g. in assembly language or C). In the latter case, the generator has to translate abstract stimulus in VHDL and possibly apply interface constraints (e.g. protocol, delays). The generator may also explicitly introduce errors.

- The *unit under test* (UUT).

- A *collector component* whose task is to collect output data from the UUT, to possibly translate them into a more readable form and to make checks. Checks can be made either by comparing the output values to ideal values defined in the component, or by comparing output values to other output values generated by a second ideal model stimulated in the same way (e.g. comparing the outputs of a RTL model and a gate-level model).

The unit under test is instantiated as a component. The stimulus and the collector components may be instantiated as components or defined as processes.

More details on test bench modeling and verification methods can be found in [Bergeron00].

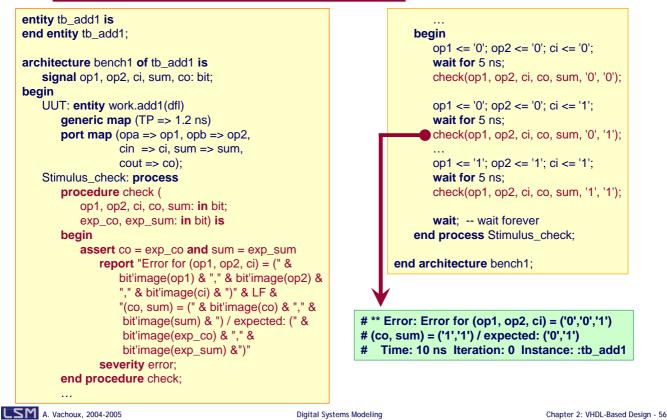

# Test bench for a 1-bit adder (1/5)

The test bench model uses a single process to define stimulus and to check the outputs. The process generates all possible input values in sequence (truth table).

The check procedure allows for verifying whether the simulated output values are equal to expected values. If not, a message is issued.

The verification uses an assert statement that also specifies a severity level. The simulator can be separately configured to react to particular severity level, e.g. to stop simulation when the severity becomes failure or error.

The 'image attribute allows for converting a value of a predefined type into a string value.

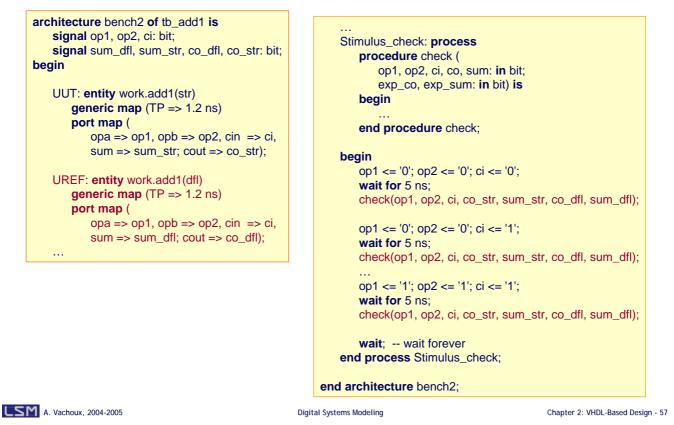

# Test bench for a 1-bit adder (2/5)

The test bench model uses a second design entity to serve as a reference model (a dataflow model). The procedure check then uses the outputs of the reference model as reference values to compare with the outputs from the unit under test (a structural gate-level model).

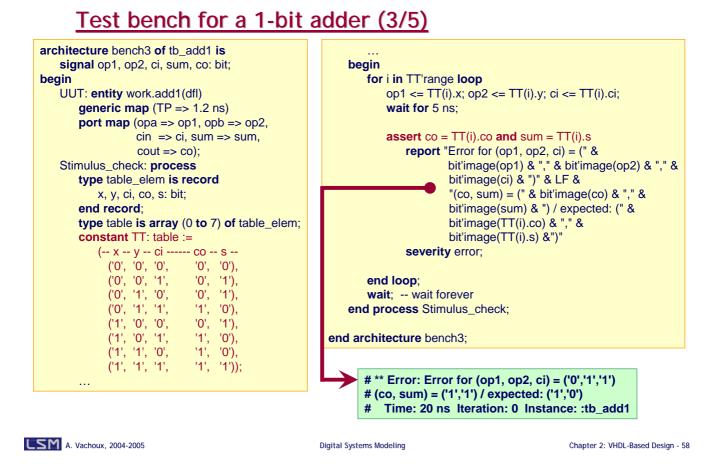

The test bench model declares the truth table of the unit to test that includes all possible inputs and their corresponding expected outputs.

The process body applies each input vector every 5 ns and then checks that the simulated output values are equal to expected values. If not, a message is issued.

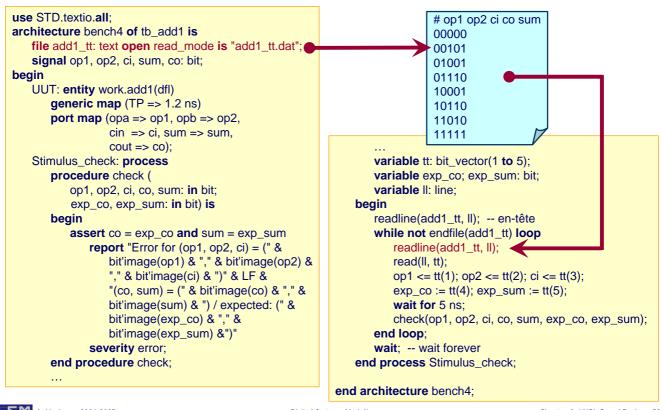

# Test bench for a 1-bit adder (4/5)

LSM A. Vachoux, 2004-2005

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 59

The truth table is now read from a file.

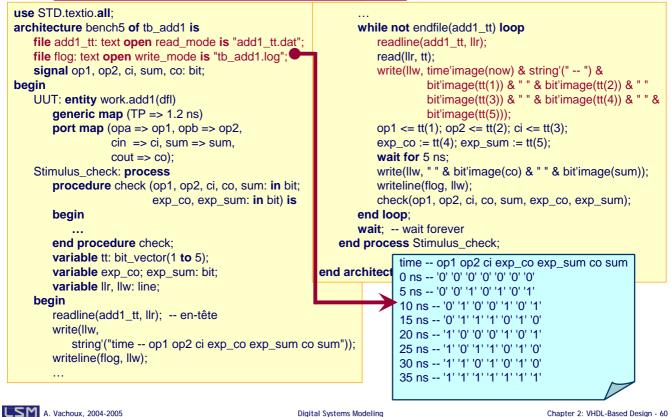

# Test bench for a 1-bit adder (5/5)

Chapter 2: VHDL-Based Design - 60

The output of the verification process is now written in a log file.

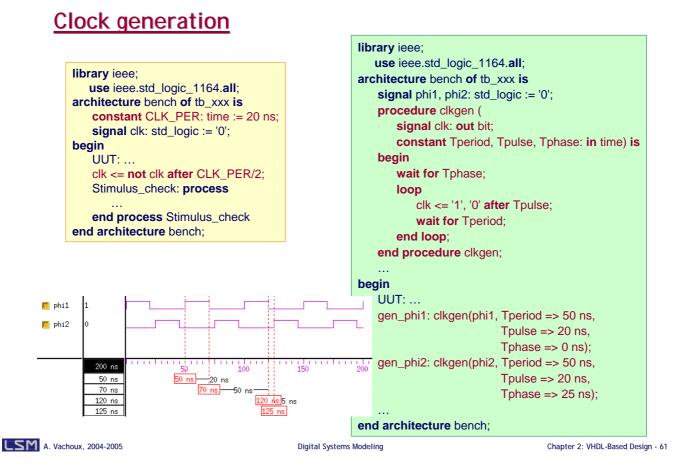

The clock behavior can be defined as a separate process (left) or as a concurrent procedure (right).

The procedure clkgen allows for defining symetrical or asymetrical clocks and then can be used to define nonoverlapping clocks. Furthermore it can be put in a package and reused in several models.

# Waveform generation (1/2) library ieee; use ieee.math\_real.all;

architecture bench of tb\_xxx is constant PC\_MIN: real := 0.3; -- % min. value ('0') constant PC\_MAX: real := 0.3; -- % max. value ('1') constant TL\_MIN : time := 5 ns; constant TL\_MAX: time := 7 ns;

**constant** TH\_MIN : time := 3 ns; **constant** TH\_MAX: time := 5 ns;

```

signal S: bit := '0';

begin

process

```

```

variable seed1: positive := 3812;

variable seed2: positive := 915;

```

Digital Systems Modeling

Chapter 2: VHDL-Based Design - 62

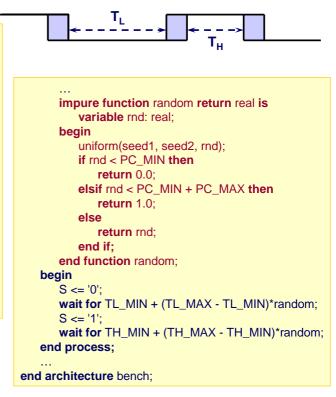

The use of the procedure uniform defined in the IEEE standard package MATH\_REAL allows for generating waveforms whose states may have random durations between some given minimum and maximum values.

The procedure uniform uses and modifies two arguments called seed1 and seed2 that control the generation of a pseudo-random sequence of values in the open interval ]0.0, 1.0[.

The function random modifies the generated random value to meet specific given percentages, namely 30% at minimum duration, 30% at maximum duration, and 40% at a random value between theses limits. The function is declared as *impure* as its execution modifies global variables (side effect). The keyword **impure** has been introduced in VHDL-1993.

# Waveform generation (2/2)

| library ieee; edu ata 0000 UUUU                        |                                                     |

|--------------------------------------------------------|-----------------------------------------------------|

| use ieee.std_logic_1164.all;                           |                                                     |

| architecture bench of tb_proc is                       |                                                     |

| constant CLK_PER: time := 10 ns; Now 0 ns              | 10 20 30 40 <b>_5D</b> 60 70                        |

| constant TSETUP : time := 3 ns;                        | 50 ns                                               |

| constant THOLD : time := 3 ns;                         | begin                                               |

| <pre>signal clk: std_logic := '0';</pre>               | wait until clk = '0';                               |

| signal rst: std_logic;                                 | wait for CLK_PER/2 - TS;                            |

| <pre>signal data: std_logic_vector(3 downto 0);</pre>  | data <= vector;                                     |

|                                                        | wait until clk = '1';                               |

| procedure do_sync_reset (                              | wait for TH;                                        |

| signal clk: in std_logic;                              | data <= ( <b>others</b> => 'X');                    |

| signal rst: out std_logic) is                          | end procedure apply_vector;                         |

| begin                                                  |                                                     |

| rst <= '0'; <b>wait until</b> clk = '0';               | begin                                               |

| rst <= '1'; <b>wait until</b> clk = '0';               | CLKGEN: clk <= not clk after CLK_PER/2;             |

| rst <= '0';                                            | DATAGEN: process begin                              |

| end procedure do_sync_reset;                           | do_sync_reset(clk,rst);                             |

|                                                        | apply_vector("0011", data);                         |

| procedure apply_vector (                               | apply_vector("1101", data);                         |

| constant vector: in std_logic_vector(3 downto          |                                                     |

| <pre>signal data : out std_logic_vector(3 downto</pre> | 0); apply_vector("1111", data, 1 ns);               |

| <b>constant</b> PER : <b>in</b> time := CLK_PER;       | apply_vector("1001", data, TH => 1 ns)              |

| <b>constant</b> TS : <b>in</b> time := TSETUP;         | wait;                                               |

| constant TH : in time := THOLD) is                     | end process DATAGEN;                                |

|                                                        | end architecture bench;                             |

| LSM A. Vachoux, 2004-2005 Digita                       | tal Systems Modeling Chapter 2: VHDL-Based Design - |

The use of procedures allows for factorizing the stimulus generation process and possibly to store these procedures in some package to favor reuse.

The procedure do\_sync\_reset performs a synchronous reset.

The procedure apply\_vector assigns a test vector to a data bus with meeting some given setup and hold times.